Laporan Percobaan 1

1. Jurnal [Kembali]

2.1 Alat dan Bahan

[Kembali]

Gambar 1. Jumper

b.Panel DL 2203D

c.Panel DL 2203C

d.Panel DL 2203S

Gambar 2. Modul De Lorenzo

2.2 Bahan Proteus

[Kembali]

b. Power DC

3. Rangkaian Simulasi

[Kembali]

4. Prinsip Kerja

[Kembali]

Pada rangkaian ini nantinya akan terjadi berbagai macam prinsip kerja yang mewakili SISO,SIPO,PISO, dan PIPO. Hal ini didapatkan berdasarkan dengan kondisi yang diberikan oleh jurnal .Pada rangkaian ini untuk inputnya dapat menjadi input yang seri dan paralel begitu juga untuk output pada rangkaian ini juga dapat menjadi output yang keluarannya seri dan paralel. maksud input/output yang seri dan paralel ini adalah

- untuk input dan output seri : data akan masuk secara bergiliran atau satu per saru dan data juga akan keluar secara bergiliran atau satu per satu

- untuk input dan output paralel : data akan masuk secara serentak dan juga keluar secara serentak

Pada rangkaian ini kan akan terjadinya pergeseran data masuk dan data keluar dari LSB ke MSB dimana sesuai dengan yang sudah dijelaskan data masuk dan keluar bisa secara bergiliran atau serentak.

Terjadinyam proses input dan output logika pada rangkaian ini juga berarti bahwa proses terjadinya register geser ini dapat menyimpan memori sementara pada masukan menuju keluaran bit ke-4 dari dearah lingkup keluaran 4 bit.

5. Video Pratikum [Kembali]

5. Video Pratikum [Kembali]

6. Analisa

[Kembali]

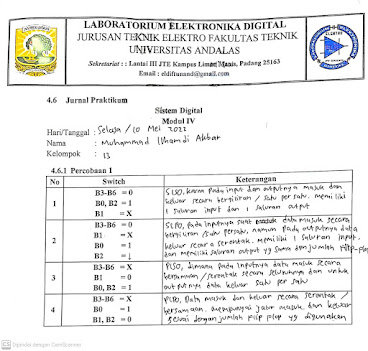

1. Analisa output yang dihasilkan tiap-tiap kondisi

- Kondisi 1

Berdasarkan output yang diperoleh terjadinya pergeseran (pada output yang masuk dari percobaan , bergeser masuk dari H4-H7). dimana LSB nya pada H7 dan MSB nya pada H4. Jadi input masuk secara berurutan dari H4-H7 dan keluar juga secara berurutan dari H7 yang keluar dulu sampai H4. Pergeseran yang berurutan ini dimulai dari LSB-MSB .Jadi berdasarkan output dari kondisi ini dapa disimpulkan bahwa kondisi 1 ini termasuk shift register yang berjenis SISO. Dimana data masuk secara berurutan dan keluar juga secara berurutan karna hanya mempunyai 1 jalur masuk dan 1 jalur keluar

- Kondisi 2

Berdasarkan output yang diperoleh ,dimana pada kondisi 2 ini termasuk shift register yang berjenis SIPO. Hal ini dkarenakan untuk output dari H4-H7 (LSB-MSB) outputnya bergeser masuk secara berurutan tetapi pada outputnya keluar secara serentak (bersamaan dari H4-H7)

- Kondisi 3

Berdasarkan output yang diperoleh, pada kondisi 3 ini termasuk dalam shift register yang berjenis PISO. Hal ini dapat dilihat dari output yang masuk pada H4-H7 (LSB-MSB) yang mana secara serentak tetapi saat ouputnya keluar outputnya akan bergeser satu per satu dari H4-H7 (dari LSB-MSB) yang keluar dahulu pada H7.

- Kondisi 4

Berdasarkan output yang diperoleh, pada kondisi 4 ini dapat disimpulkan termasuk dalam shift register berjenis PIPO hal ini dikarenakan output yang masuk pada (H4-H7)(LSB-MSB) masuk secara serentak dan juga untuk outputnya keluar juga secara serentak

2. Jika gerbang AND pada rangkaian dihapus, sumber clock dihubungkan langsung ke flip flop, bandingkan output yang didapatkan

- Untuk kondisi 1 dan 2

Pada dua kondisi ini output yang dihasilkan adalah 4 flip flop berada dalam kondisi set hal ini dikarenakan B3-B6 diatur berlogika 0 sehingga mengaktifkan pin set pada JK flip flop yang aktif saat berlogika 0. yang membuat output pada logic probe berlogika 1 semuanya (1111)

- Untuk Kondisi 3 dan 4

pada dua kondisi ini output yang dihasilkan ada 2 yaitu:

a. Saat B3-B6 diberi logika 1 maka rangkaian dalam kondisi tetap sehingga jika kita ingin melihat output yang keluar kita mengatur saklar B1 menjadi logika 1 dan 0 nantinya akan terbentuk rangkaian shift register SISO

b. Saat B3-B6 diatur berlogika 0, maka rangkaian flip flop berada dalam kondisi set (berlogika 1) hal ini dikarenakan pin set aktif tetapi karna pergantian ini terjadi secara serentak dapat digolongkan pada rangkaian shift register PIPO.

7. Link Download

[Kembali]

Download HTML DISINI

Download File Rangkaian DISINI

Download Video Percobaan DISINI

Download Datasheet IC 74111 DISINI

Download Datasheet Gerbang NOT DISINI

Download Datasheet Gerbang AND DISINI

Download Datasheet Switch DISINI

Download Datasheet LogicProbe DISINI

Tidak ada komentar:

Posting Komentar